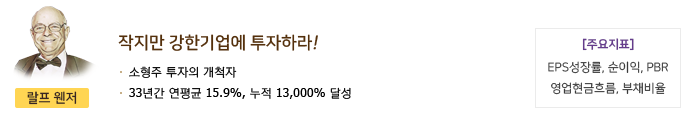

랄프 웬저 -매커스

투자대가의 철학과 검증된 투자방법을 계랑화해 대가가 관심을 가질만한

상장기업 전체의 투자매력도 순위를 제공합니다.

- HOME

- 대가 추천주

- 랄프 웬저

9,800원

▲60▲0.62%

04/25 09:24 현재

04/25 09:24 현재

|

|

매커스 |  |

|---|---|---|---|

|

|

1.3 | |

|

|

246% | |

|

|

67.6% | |

|

|

1,440% | |

|

|

1,264억 |

| 항목 | 2022.9 | 2021.12 | 2020.12 |

|---|---|---|---|

| 매출액 | 1,391 | 1,285 | 802 |

| 영업이익 | 262 | 204 | 93 |

| 영업이익률 | 18.8% | 15.9% | 11.6% |

| 순이익 | 170 | 250 | 80 |

| 순이익률 | 12.2% | 19.5% | 10% |

| 기업개요 | 비메모리 반도체 PLD(Programmable Logic Device) 솔루션 업체 |

|---|---|

| 사업환경 | ▷ 반도체 설계는 복잡해지는 반면 제품 수명은 단축되고 있어 PLD 반도체 수요는 증가할 것으로 전망 ▷ PLD 반도체 일종인 FPGA는 시스템의 메인프로세서로 활용되는 추세 |

| 경기변동 | ▷ IT산업 경기동향과 반도체산업 경기에 영향을 받음 |

| 주요제품 | 비메모리 반도체 등 94.51% 스토리지 등 3.96% 영업수익 1.17% 기타 0.35% 매커스(기타) 0.02% * 수치는 매출 비중 |

| 원재료 | ▷ FPGA 반도체, 아날로그 반도체 등 * 괄호 안은 매입 비중 |

| 실적변수 | ▷ 자일링스(Xilinx)사의 PLD 제품 인지도 상승시 수혜 ▷ IT제품 개발 주기 단축시 수혜 |

| 리스크 | 재무건전성 ★★★★ - 부채비율 181.96% - 유동비율 150.12% - 당좌비율 39.17% - 이자보상배율 8,602.90% - 자본유보율 1,103.95% |

| 신규사업 | ▷ 진행 중인 신규사업 없음 |