ЦэС§РкСж | VТїЦЎ(Value Chart) ПьЗЎСжДТ РчЙЋКаМЎ ЕЕБИРЮ 'VТїЦЎ'ИІ ХыЧи НЧРћАњ РчЙЋ ОШРќМКРЬ ПьЗЎЧб БтОїРЛ МвАГЧЯДТ ФкГЪРдДЯДй. VТїЦЎДТ ОЦРЬХѕРкПЁМ РкУМ АГЙпЧб РчЙЋКаМЎ ЕЕБИЗЮ РчЙЋСІЧЅИІ ТїЦЎЗЮ КаМЎЧв Мі РжЕЕЗЯ ИИЕч АЭРдДЯДй.

ИХФПНКДТ КёИоИ№ИЎ ЙнЕЕУМ МжЗчМЧ ОїУМДй. БлЗЮЙњ ЙнЕЕУМ РќЙЎШИЛч СІЧАРЛ БЙГЛПЁ ЕщПЉПЭ ЦЧИХЧЯДТ ДыИЎСЁ ЧќХТРЧ ЛчОїРЛ ПюПЕЧЯАэ РжДй. ДйИИ, ИХФПНКДТ ДмМјШї ЛѓЧАРЛ ЦФДТ РЏХыШИЛчРЧ ПЊЧвПЁ БзФЁСі ОЪАэ АэАДЛчРЧ СІЧА АГЙп ДмАшПЁ ТќПЉЧи МжЗчМЧРЛ СІАјЧбДй. ИХФПНКРЧ ЦФЦЎГЪЛчДТ XILINX(РкРЯИЕНК)ПЭ Intersil(РЮХЭНЧ) ЕюРЬДй.ЙнЕЕУМДТ ИоИ№ИЎПЭ КёИоИ№ИЎЗЮ БИКаЕШДй. СЄКИ РњРхРЬ ИёРћРЮ ИоИ№ИЎ ЙнЕЕУМПЭ ДоИЎ КёИоИ№ИЎ ЙнЕЕУМДТ СЄКИ УГИЎАЁ ИёРћРЬДй. КёИоИ№ИЎ ЙнЕЕУМ СпПЁМЕЕ PLDПЭ Analog ICПЭ ААРК НУНКХл ЙнЕЕУМАЁ ИХФПНКРЧ СжЗТ ЛѓЧАРЬДй.

IoTПЭ РкРВСжЧрТї Ею 4Тї ЛъОїПЁ ДыЧб АќНЩРЬ ГєОЦСіИщМ КёИоИ№ИЎ ЙнЕЕУМРЧ СпПфМКРЬ КЮАЂЕЧАэ РжДй. КёИоИ№ИЎДТ МіРд РЧСИЕЕАЁ ГєРК ИИХ ИХФПНКПЁ ДыЧб НУРхРЧ АќНЩРЬ ФПСіАэ РжДй.

ЂЙ 2017Гт ИХУтОз РќГтКё +29%, КёИоИ№ИЎ ЙнЕЕУМ МіПфЁш

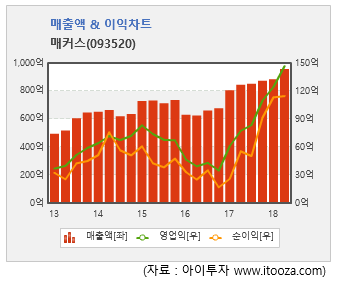

ИХФПНКРЧ УжБй НЧРћ ЦЏТЁРК 2017Гт ИХУт СѕАЁДй. 2017Гт ИХУтОзРК 874ОяПј(РЬЧЯ ПЌАсРчЙЋСІЧЅ БтСи)РИЗЮ 2016Гт 677ОяПј ДыКё 29% ДУОњДй. ААРК БтАЃ ЛѓЧА ИХУтРЬ 30% АЁЗЎ СѕАЁЧи РќУМ ИХУт МКРхРЛ АпРЮЧпДй.

ИХФПНКРЧ ИХУтРК ЦФЦЎГЪЛчРЮ РкРЯИЕНКРЧ РЮСіЕЕПЁ ПЕЧтРЛ ЙоДТДй. ИХФПНК ИХУтРЧ 90%АЁ РкРЯИЕНК СІЧА ЦЧИХПЁМ ЙпЛ§ЧбДй. УжБй 4Тї ЛъОїРЬ СжИё ЙоРИИщМ РкРЯИЕНКРЧ FPGA МіПфАЁ СѕАЁЧпДй. РкРЯИЕНКДТ FPGAИІ Л§ЛъЧЯДТ БлЗЮЙњ ДыЧЅ БтОїРЬДй. КёИоИ№ИЎ ЙнЕЕУМ НУРхПЁМ 50%АЁ ГбДТ СЁРЏРВРЛ АЁСјДй. СіГЧи ШПўРЬПЭ ОЫИЎЙйЙй ЕюРЧ БлЗЮЙњ БтОїРЧ ХЌЖѓПьЕх МКёНКПЁ РкРЯИЕНКРЧ FPGAАЁ УЄХУЕЧИч АцРяЗТРЛ РдСѕЧпДй.

FPGAДТ КёИоИ№ИЎ ЙнЕЕУМРЧ Чб СОЗљДй. РЯЙнРћРИЗЮ ЙнЕЕУМДТ ЧбЙј ЧСЗЮБзЗЁЙжРЬ ПЯЗсЕЧИщ ШИЗЮ МіСЄРЬ КвАЁДЩЧЯДй. БзЗЏГЊ FPGAДТ ЛчПыРкАЁ ПыЕЕПЁ ИТАд ПЉЗЏТїЗЪ ШИЗЮИІ КЏАцЧв Мі РжДй. Ся, ПРЗљАЁ ЙпЛ§ЧиЕЕ МіСЄРЬ АЁДЩЧЯДй. ЖЇЙЎПЁ НХСІЧА АГЙп БтАЃРЬ ТЊОЦСј IT НУРхПЁМ FPGA МіПфАЁ ДУАд ЕЦДй. FPGA ЙнЕЕУМДТ ДыЗЎ Л§ЛъЕЧДТ DЗЅАњ CPU ЕюАњ ДоИЎ СжЙЎЧќ ЙнЕЕУМЗЮ БИИХРкПЭРЧ АшОрРЛ ХыЧи АЁАнРЬ АсСЄЕЧДТ ЦЏМКРЬ РжДй.

FPGAАЁ НУРхРЧ АќНЩРЛ ВєДТ ЖЧ ДйИЅ РЬРЏДТ ЧбАшПЁ ЕЕДоЧб ЙќПы ЧСЗЮМММ МКДЩПЁ РжДй. ЕіЗЏДз БтМњАњ РкРВСжЧрТї Ею ЙЬЗЁ ЛъОїРЬ АЂБЄ ЙоРИИщМ ЙцДыЧб РкЗсИІ КќИЃАэ СЄШЎЧЯАд УГИЎЧЯДТ ПЌЛъ МгЕЕАЁ СпПфЧиСГДй. FPGAДТ CPUКИДй ИЙРК ОчРЧ ЕЅРЬХЭ УГИЎАЁ АЁДЩЧЯДй. FPGAАЁ CPUПЭ ЧдВВ КДЗФ ФФЧЛЦУПЁ ЛчПыЕЧИщ ИЙРК ОчРЧ СЄКИИІ ШПРВРћРИЗЮ УГИЎЧв Мі РжАд ЕШДй. КДЗФ ФФЧЛЦУРК ПЉЗЏ АГ ЧСЗЮММНКИІ ЧбЙјПЁ УГИЎЧЯБт РЇЧи АэОШЕШ АГГфРИЗЮ НДЦлФФЧЛХЭАЁ ДыЧЅРћРЮ ЛчЗЪДй.

МіРдПЁ РЧСИЧЯДТ БЙГЛ КёИоИ№ИЎ ЙнЕЕУМ НУРхЕЕ ИХФПНК ИХУтПЁ БрСЄРћРЮ ПЕЧтРЛ ЙЬУЦДй. ММАш ЙнЕЕУМ ЙЋПЊ ХыАш БтБИПЁ ЕћИЃИщ 2017Гт РќУМ ЙнЕЕУМ ИХУтРК 4122Оя ДоЗЏДй. КёИоИ№ИЎ ЙнЕЕУМ ИХУтРК 2882Оя ДоЗЏЗЮ РќУМ ЙнЕЕУМ НУРхРЧ 69.9%ИІ ТїСіЧбДй. БзЗЏГЊ БлЗЮЙњ КёИоИ№ИЎ ЙнЕЕУМ НУРхПЁМ БЙГЛ ЛъОїРЧ КёСпРК 3% СЄЕЕЗЮ УыОрЧЯДй. ITСІЧАПЁ УЄПыЕЧДТ ДыКЮКаРЧ КёИоИ№ИЎ ЙнЕЕУМ СІЧАРК МіРдПЁ РЧСИЧв Мі ЙлПЁ ОјДй.

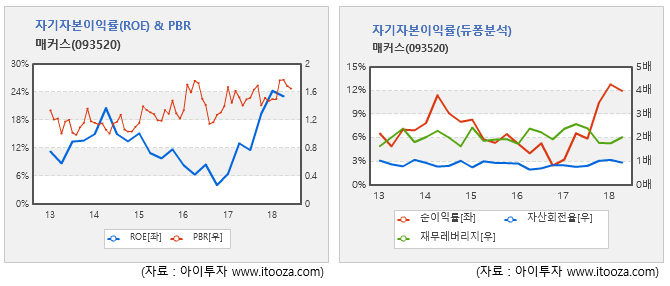

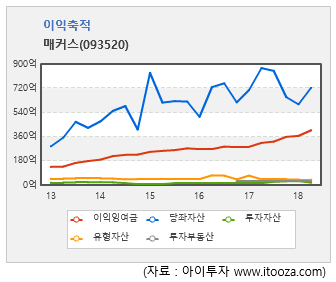

ЂЙ МјРЬРЭЗќ АГМБПЁ ROE ЛѓНТ

2016Гт 4.0%ПДДј ROEДТ 2017Гт 19.3%ИІ БтЗЯЧбДй. МјРЬРЭЗќРЬ ХЋ ЦјРИЗЮ АГМБЕЧИщМ ROE ЛѓНТРЛ РЬВјОњДй. МјРЬРЭЗќРК ИХУтОз ДыКё МјРЬРЭРЧ КёРВРЛ РЧЙЬЧбДй. 2016Гт ИХУтАњ РЬРЭ АЈМвЗЮ 2.4%БюСі ЧЯЖєЧпДј МјРЬРЭЗќРК 2017Гт ИХУтАњ РЬРЭРЬ СѕАЁЧб ДіКаПЁ 10.4%ЗЮ ПУЖњДй.

УбРкЛъШИРќРВАњ РчЙЋЗЙЙіИЎСіДТ ЛѓДыРћРИЗЮ КЏШАЁ РћДй. РкЛъ БдИ№ ДыКё ИХУтОз КёРВРЛ РЧЙЬЧЯДТ УбРкЛъШИРќРВРК СіГ 5ГтАЃ 0.6ЙшПЁМ 1.0Йш ЛчРЬИІ РЏСіЧЯАэ РжДй. ЙнИщ, РчЙЋЗЁЙіИЎСіДТ 2016Гт 1.9ЙшПЁМ 1.7ЙшЗЮ ЧЯЖєЧпДй. ТїРдБнРЛ ЛѓШЏЧи КЮУЄАЁ СйОюЕч ЙнИщ ИХУтРК СѕАЁЧпБт ЖЇЙЎРЬДй.

ЂЙ 2017Гт ТїРдБн КёСп 3.2%, РчЙЋЛѓХТ 'ОШРќ'

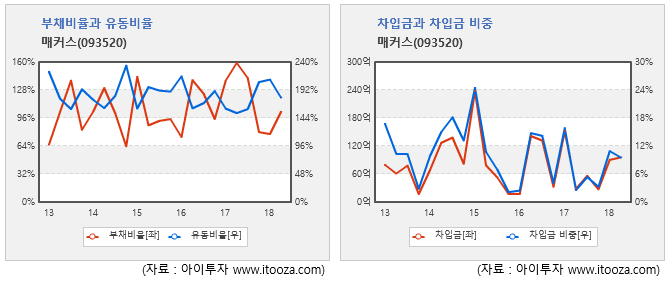

РчЙЋЛѓХТДТ ОШРќЧЯДй. 2017Гт БтСи КЮУЄКёРВРК 80%, РЏЕПКёРВРЛ 205%Дй. РкЛъ ДыКё ТїРдБн КёСпРК 3.2%Дй. ТїРдБн(27ОяПј)РИЗЮКЮХЭ ЙпЛ§ЧЯДТ РЬРкДТ Ор 1ОяПјРИЗЮ ПЕОїРЬРЭРЬ 110ОяПјРгРЛ АэЗСЧЯИщ КЮДуНКЗЏПю МіСиРЬ ОЦДЯДй.

2017Гт КЮУЄРЧ ДыКЮКаРК ИХРдУЄЙЋПЁМ ЙпЛ§ЧпДй. Уб КЮУЄ 379ОяПј Сп 330ОяПјРЬ ИХРдУЄЙЋДй. ИХРдУЄЙЋДТ СІЧАРЛ ЙоАэ ЙЬСіБоЧб ЕЗРИЗЮ РЬРкАЁ ЙпЛ§ЧЯСі ОЪДТ КЮУЄДй. 2018Гт 2КаБт БтСи ИХРдУЄЙЋДТ 392ОяПјРИЗЮ СѕАЁЧпДй. ИХРдУЄЙЋ ШИРќРЯМіДТ 2017Гт БтСи 138РЯПЁМ 2018Гт 2КаБт 151РЯЗЮ ДУОњДй. РЬДТ ИХФПНКАЁ БИРд ДыБнРЛ 150РЯ РЬГЛПЁ СіБоЧЯАэ РжРНРЛ РЧЙЬЧбДй.

ЧіБнМК РкЛъЕЕ ЧГКЮЧЯДй. 2016Гт 94ОяПјРЬДј ЧіБнЙзЧіБнМКРкЛъРК 2017Гт 170ОяПј, 2018Гт 2КаБт 199ОяПјРИЗЮ ДУОњДй. 2018Гт 1КаБт БтСи МјЧіБнМК РкЛъ(ЧіБнЙзЧіБнМКРкЛъ + ДмБтБнРЖЛѓЧА - ТїРдБн)РК 137ОяПј РЬДй. ИХФПНКДТ КёИоИ№ИЎ ЙнЕЕУМИІ СїСЂ СІСЖЧЯСі ОЪДТДй. РЏХыОїПЁ АЁБюПю ЛчОїРИЗЮ РкЛъ БИСЖАЁ РЯЙнРћРЮ СІСЖОїУМПЭДТ ДйИЃДй. РќУМ РкЛъ Сп РЏЧќРкЛъРЬ ТїСіЧЯДТ КёСпРК 2018Гт 2КаБт БтСи 4.1%ЗЮ ГЗДй. ДыБдИ№ МГКёХѕРкАЁ ЧЪПфЧЯСі ОЪОЦ РЬРЭРЬ ЧіБнРИЗЮ НзРЮДй.

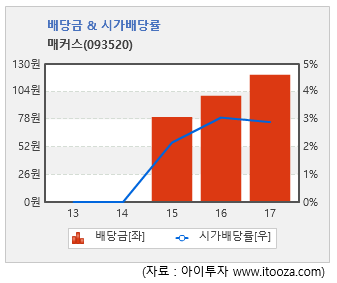

ЂЙ ЙшДчБн ШЎДы, 2016Гт 100Пј Ёц 2017Гт 120Пј

ИХФПНКДТ 2015ГтКЮХЭ ЙшДчБнРЛ ЧиИЖДй 20ПјОП ДУИЎАэ РжДй. 2015Гт 80ПјРЬДј СжДч ЙшДчБнРК 2016Гт 100Пј, 2017Гт 120ПјРИЗЮ ДУОњДй. 2017Гт БтСи НУАЁЙшДчЗќРК 2.9%Дй. ИИОр ПУЧиЕЕ РќГтАњ ЕПРЯЧЯАд 20ПјРЛ ДУЗС СжДч 140ПјРЛ ЙшДчЧв ЖЇ БтДыЧв Мі РжДТ ЙшДчМіРЭЗќРК 2.7%(3РЯ СОАЁ БтСи)Дй.

3РЯ ИХФПНКДТ РќРЯ ДыКё 2.1% ПРИЅ 5180ПјПЁ РхРЛ ИЖАЈЧпДй. 3РЯ СОАЁПЭ ПУЧи 2КаБт ПЌШЏЛъ НЧРћРЛ ЙнПЕЧб СжАЁМіРЭЙшМі(PER)ДТ 7.1Йш, СжАЁМјРкЛъЙшМі(PBR)ДТ 1.65Йш РкБтРкКЛРЬРЭЗќ(ROE)РК 23.0%Дй.

ЧбЦэ РкРЯИЕНКАЁ КёЦЎФкРЮ УЄБМ РќПы МжЗчМЧРЛ АЎУс ЙнЕЕУМИІ Л§ЛъЧЯИщМ ИХФПНКЕЕ КёЦЎФкРЮ АќЗУСжПЁ АХЗаЕШ Йй РжДй. КёЦЎФкРЮ АќЗУ МвНФПЁ ИХФПНК СжАЁЕЕ БоЕюЖєЧв Мі РжДТ СЁРК РЏРЧЧв КЮКаРЬДй.

ЧСИАЦЎ

ЧСИАЦЎ РЬИоРЯ

РЬИоРЯ КэЗЮБз ДуБт

КэЗЮБз ДуБт СЁМіСжБт

СЁМіСжБт

(ДёБл 0АГ)

(ДёБл 0АГ)