м•„мқҙнҲ¬мһҗ лүҙмҠӨ > м „мІҙ

м•„мқҙнҲ¬мһҗ м „мІҙ News кёҖмһ…лӢҲлӢӨ.

[мҰүмӢң분м„қ] л§Өм»ӨмҠӨ, мӢӨм Ғк°ңм„ м—җлҸ„ мЈјк°Җ н•ҳлқҪ...PER 8л°°

л§Өм»ӨмҠӨ21,800мӣҗ, в–ј-150мӣҗ, -0.68%мқҳ мӢӨм Ғмқҙ к°ңм„ лҗҗмқҢм—җлҸ„ мЈјк°ҖлҠ” н•ҳлқҪн•ҳкі мһҲм–ҙ лҲҲкёёмқ„ лҒҲлӢӨ. 10мқј мҳӨнӣ„ 1мӢң 26분 нҳ„мһ¬ л§Өм»ӨмҠӨлҠ” м „мқј лҢҖ비 0.8%(25мӣҗ) лӮҙлҰ° 3070мӣҗмқ„ кё°лЎқ мӨ‘мқҙлӢӨ. мЈјк°ҖлҠ” мӢӨм Ғ л°ңн‘ңмқј(5мӣ” 14мқј) мў…к°Җ 3660мӣҗм—җм„ң м•Ҫ 3мЈј л§Ңм—җ 16% н•ҳлқҪн–ҲлӢӨ.

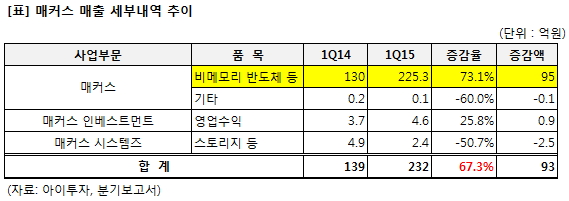

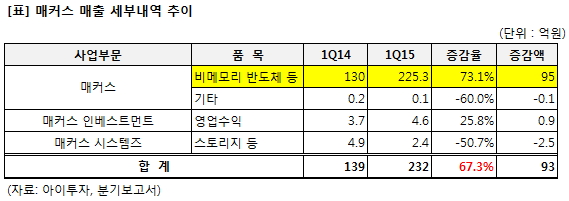

м§ҖлӮң 14мқј л°ңн‘ңн•ң л§Өм»ӨмҠӨмқҳ м§ҖлӮң 1분기 м—°кІ° кё°мӨҖ л§Өм¶ңм•ЎмқҖ 232м–өмӣҗмңјлЎң м „л…„ лҸҷкё° лҢҖ비 67.3%(94м–өмӣҗ) лҠҳм—ҲлӢӨ. мҳҒм—…мқҙмқөмқҖ 26м–өмӣҗмңјлЎң 72.3%, м§Җл°°м§Җ분 мҲңмқҙмқөмқҖ 21м–өмӣҗмңјлЎң 88.9% мҰқк°Җн–ҲлӢӨ.

PLD л°ҳлҸ„мІҙ л“ұ 비메лӘЁлҰ¬ л°ҳлҸ„мІҙ мғҒн’Ҳл§Өм¶ңмқҙ л§Өм¶ңм•Ў мғҒмҠ№мқ„ мқҙлҒҲ кІғмңјлЎң н’ҖмқҙлҗңлӢӨ. 비메лӘЁлҰ¬ л°ҳлҸ„мІҙ мғҒн’Ҳл§Өм¶ңм•ЎмқҖ 225м–өмӣҗмңјлЎң м „л…„ лҸҷкё°(130м–ө) лҢҖ비 95м–өмӣҗ(73.1%) мҰқк°Җн–ҲлӢӨ. л§Өм»ӨмҠӨлҠ” 비메лӘЁлҰ¬ л°ҳлҸ„мІҙ л“ұ л°ҳлҸ„мІҙ мғҒн’Ҳл§Өм¶ңмқҙ л§Өм¶ң비мӨ‘мқҳ 97%лҘј м°Ём§Җн•ңлӢӨ.

мҳҒм—…мқҙмқөмқҖ 26м–ө2000л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё°(15м–ө2000л§Ңмӣҗ) лҢҖ비 72.9% лҠҳм–ҙ л§Өм¶ңм•Ў мҰқк°ҖмңЁмқ„ мғҒнҡҢн–ҲлӢӨ. м§ҖлӮң н•ҙ л°ңмғқн–ҲлҚҳ мҲҳм„ л№„ 1м–ө2000л§Ңмӣҗмқҙ мҳ¬н•ҙлҠ” кё°лЎқлҗҳм§Җ м•ҠлҠ” л“ұ 1분기 нҢҗкҙҖ비лҠ” 12.5% лҠҳм–ҙ нҢҗкҙҖ비 мҰқк°ҖмңЁмқҙ л§Өм¶ңм•Ў мҰқк°ҖмңЁ(67.3%)м—җ нҒ¬кІҢ лӘ» лҜёміӨлӢӨ. к·ё кІ°кіј нҢҗкҙҖ비мңЁмқҖ 8.6%лЎң м „л…„ лҸҷкё° лҢҖ비 4.2%P к°җмҶҢн•ҙ мҳҒм—…мқҙмқө к°ңм„ нҸӯмқҙ лҠҳм—ҲлӢӨ.

м§Җл°°м§Җ분 мҲңмқҙмқөмқҖ 20м–ө5000л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё° лҢҖ비 88.9% лҠҳм—ҲлӢӨ. мҷёнҷ” кҙҖл Ё мқҙмқөмқҙ лҠҳл©ҙм„ң кё°нғҖмҶҗмқөмқҙ -3000л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё°(-3м–өмӣҗ) лҢҖ비 2м–ө7000л§Ңмӣҗ к°ңм„ лҗҗлӢӨ. кёҲмңөмҶҗмқөмқҖ 300л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё° лҢҖ비 1м–ө3000л§Ңмӣҗ к°җмҶҢн–ҲлӢӨ.

л§Өм»ӨмҠӨлҠ” 비메лӘЁлҰ¬ л°ҳлҸ„мІҙмқё PLD(Programmable Logic Device) л°ҳлҸ„мІҙмҷҖ м•„лӮ лЎңк·ё л°ҳлҸ„мІҙ л“ұмқ„ кё°мҲ мҳҒм—…мқ„ нҶөн•ҙ мң нҶөн•ңлӢӨ. н•ҙмҷё л°ҳлҸ„мІҙ м—…мІҙмқё мһҗмқјл§ҒмҠӨ(Xilinx), мқён„°мӢӨ(Intersil) л“ұмқ„ нҢҢнҠёл„ҲлЎң ліҙмң н•ҳкі мһҲмңјл©° көӯлӮҙ м•Ҫ 500м—¬ ITм—…мІҙм—җ мғҒн’Ҳмқ„ лӮ©н’Ҳн•ҳкі мһҲлӢӨ.

л§Өм»ӨмҠӨлҠ” м „м„ёкі„ мӢңмһҘ 50~55%лҘј м җмң н•ҳлҠ” PLDл°ҳлҸ„мІҙмқҳ м„ лҸ„м—…мІҙмқё мһҗмқјл§ҒмҠӨ(Xilinx)мҷҖ кіөкёүкі„м•Ҫмқ„ мІҙкІ°н•ҳкі мһҲлӢӨ. мЈјл Ҙ м ңн’Ҳмқё Xilinx PLDлҠ” лӘЁл“ кё°лҠҘмқҙ мӮ¬м „м—җ н”„лЎңк·ёлһЁ лҸј л§Ңл“Өм–ҙм§ҖлҠ” мЈјл¬ёнҳ• л°ҳлҸ„мІҙмҷҖ лӢ¬лҰ¬ мӮ¬мҡ©мһҗк°Җ мһҗмң лЎӯкІҢ л°ҳлҸ„мІҙ 칩мқҙ мҲҳн–үн•ҳлҠ” кё°лҠҘмқ„ м„Өкі„н•ҳкі ліҖкІҪн• мҲҳ мһҲм–ҙ кі к°қмқҳ м ңн’Ҳ к°ңл°ңм—җ мҶҢмҡ”лҗҳлҠ” мӢңк°„кіј 비мҡ©мқ„ мӨ„мқј мҲҳ мһҲлӢӨ.

1분기 мӢӨм Ғмқ„ л°ҳмҳҒн•ң л§Өм»ӨмҠӨмқҳ мЈјк°ҖмҲҳмқөл°°мҲҳ(PER)лҠ” 8.23л°°лӢӨ. мЈјк°ҖмҲңмһҗмӮ°л°°мҲҳ(PBR)лҠ” 1.25л°°, мһҗкё°мһҗліёмқҙмқөлҘ (ROE)мқҖ 15.1%лӢӨ.

[2015л…„ 3мӣ” 31мқј кё°мӨҖ, лӢЁмң„ : мЈјмӢқмҲҳ(мЈј), м§Җ분мңЁ(%)]

м§ҖлӮң 14мқј л°ңн‘ңн•ң л§Өм»ӨмҠӨмқҳ м§ҖлӮң 1분기 м—°кІ° кё°мӨҖ л§Өм¶ңм•ЎмқҖ 232м–өмӣҗмңјлЎң м „л…„ лҸҷкё° лҢҖ비 67.3%(94м–өмӣҗ) лҠҳм—ҲлӢӨ. мҳҒм—…мқҙмқөмқҖ 26м–өмӣҗмңјлЎң 72.3%, м§Җл°°м§Җ분 мҲңмқҙмқөмқҖ 21м–өмӣҗмңјлЎң 88.9% мҰқк°Җн–ҲлӢӨ.

PLD л°ҳлҸ„мІҙ л“ұ 비메лӘЁлҰ¬ л°ҳлҸ„мІҙ мғҒн’Ҳл§Өм¶ңмқҙ л§Өм¶ңм•Ў мғҒмҠ№мқ„ мқҙлҒҲ кІғмңјлЎң н’ҖмқҙлҗңлӢӨ. 비메лӘЁлҰ¬ л°ҳлҸ„мІҙ мғҒн’Ҳл§Өм¶ңм•ЎмқҖ 225м–өмӣҗмңјлЎң м „л…„ лҸҷкё°(130м–ө) лҢҖ비 95м–өмӣҗ(73.1%) мҰқк°Җн–ҲлӢӨ. л§Өм»ӨмҠӨлҠ” 비메лӘЁлҰ¬ л°ҳлҸ„мІҙ л“ұ л°ҳлҸ„мІҙ мғҒн’Ҳл§Өм¶ңмқҙ л§Өм¶ң비мӨ‘мқҳ 97%лҘј м°Ём§Җн•ңлӢӨ.

мҳҒм—…мқҙмқөмқҖ 26м–ө2000л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё°(15м–ө2000л§Ңмӣҗ) лҢҖ비 72.9% лҠҳм–ҙ л§Өм¶ңм•Ў мҰқк°ҖмңЁмқ„ мғҒнҡҢн–ҲлӢӨ. м§ҖлӮң н•ҙ л°ңмғқн–ҲлҚҳ мҲҳм„ л№„ 1м–ө2000л§Ңмӣҗмқҙ мҳ¬н•ҙлҠ” кё°лЎқлҗҳм§Җ м•ҠлҠ” л“ұ 1분기 нҢҗкҙҖ비лҠ” 12.5% лҠҳм–ҙ нҢҗкҙҖ비 мҰқк°ҖмңЁмқҙ л§Өм¶ңм•Ў мҰқк°ҖмңЁ(67.3%)м—җ нҒ¬кІҢ лӘ» лҜёміӨлӢӨ. к·ё кІ°кіј нҢҗкҙҖ비мңЁмқҖ 8.6%лЎң м „л…„ лҸҷкё° лҢҖ비 4.2%P к°җмҶҢн•ҙ мҳҒм—…мқҙмқө к°ңм„ нҸӯмқҙ лҠҳм—ҲлӢӨ.

м§Җл°°м§Җ분 мҲңмқҙмқөмқҖ 20м–ө5000л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё° лҢҖ비 88.9% лҠҳм—ҲлӢӨ. мҷёнҷ” кҙҖл Ё мқҙмқөмқҙ лҠҳл©ҙм„ң кё°нғҖмҶҗмқөмқҙ -3000л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё°(-3м–өмӣҗ) лҢҖ비 2м–ө7000л§Ңмӣҗ к°ңм„ лҗҗлӢӨ. кёҲмңөмҶҗмқөмқҖ 300л§ҢмӣҗмңјлЎң м „л…„ лҸҷкё° лҢҖ비 1м–ө3000л§Ңмӣҗ к°җмҶҢн–ҲлӢӨ.

л§Өм»ӨмҠӨлҠ” 비메лӘЁлҰ¬ л°ҳлҸ„мІҙмқё PLD(Programmable Logic Device) л°ҳлҸ„мІҙмҷҖ м•„лӮ лЎңк·ё л°ҳлҸ„мІҙ л“ұмқ„ кё°мҲ мҳҒм—…мқ„ нҶөн•ҙ мң нҶөн•ңлӢӨ. н•ҙмҷё л°ҳлҸ„мІҙ м—…мІҙмқё мһҗмқјл§ҒмҠӨ(Xilinx), мқён„°мӢӨ(Intersil) л“ұмқ„ нҢҢнҠёл„ҲлЎң ліҙмң н•ҳкі мһҲмңјл©° көӯлӮҙ м•Ҫ 500м—¬ ITм—…мІҙм—җ мғҒн’Ҳмқ„ лӮ©н’Ҳн•ҳкі мһҲлӢӨ.

л§Өм»ӨмҠӨлҠ” м „м„ёкі„ мӢңмһҘ 50~55%лҘј м җмң н•ҳлҠ” PLDл°ҳлҸ„мІҙмқҳ м„ лҸ„м—…мІҙмқё мһҗмқјл§ҒмҠӨ(Xilinx)мҷҖ кіөкёүкі„м•Ҫмқ„ мІҙкІ°н•ҳкі мһҲлӢӨ. мЈјл Ҙ м ңн’Ҳмқё Xilinx PLDлҠ” лӘЁл“ кё°лҠҘмқҙ мӮ¬м „м—җ н”„лЎңк·ёлһЁ лҸј л§Ңл“Өм–ҙм§ҖлҠ” мЈјл¬ёнҳ• л°ҳлҸ„мІҙмҷҖ лӢ¬лҰ¬ мӮ¬мҡ©мһҗк°Җ мһҗмң лЎӯкІҢ л°ҳлҸ„мІҙ 칩мқҙ мҲҳн–үн•ҳлҠ” кё°лҠҘмқ„ м„Өкі„н•ҳкі ліҖкІҪн• мҲҳ мһҲм–ҙ кі к°қмқҳ м ңн’Ҳ к°ңл°ңм—җ мҶҢмҡ”лҗҳлҠ” мӢңк°„кіј 비мҡ©мқ„ мӨ„мқј мҲҳ мһҲлӢӨ.

1분기 мӢӨм Ғмқ„ л°ҳмҳҒн•ң л§Өм»ӨмҠӨмқҳ мЈјк°ҖмҲҳмқөл°°мҲҳ(PER)лҠ” 8.23л°°лӢӨ. мЈјк°ҖмҲңмһҗмӮ°л°°мҲҳ(PBR)лҠ” 1.25л°°, мһҗкё°мһҗліёмқҙмқөлҘ (ROE)мқҖ 15.1%лӢӨ.

[л§Өм»ӨмҠӨ] нҲ¬мһҗ мІҙнҒ¬ нҸ¬мқёнҠё

| кё°м—…к°ңмҡ” | 비메лӘЁлҰ¬ л°ҳлҸ„мІҙ PLD(Programmable Logic Device) мҶ”лЈЁм…ҳ м—…мІҙ |

|---|---|

| мӮ¬м—…нҷҳкІҪ | в–· л°ҳлҸ„мІҙ м„Өкі„лҠ” ліөмһЎн•ҙм§ҖлҠ” л°ҳл©ҙ м ңн’Ҳ мҲҳлӘ…мқҖ лӢЁм¶•лҗҳкі мһҲм–ҙ PLD л°ҳлҸ„мІҙ мҲҳмҡ”лҠ” мҰқк°Җн• кІғмңјлЎң м „л§қ в–· PLD л°ҳлҸ„мІҙ мқјмў…мқё FPGAлҠ” мӢңмҠӨн…ңмқҳ л©”мқён”„лЎңм„ём„ңлЎң нҷңмҡ©лҗҳлҠ” 추세 |

| кІҪкё°ліҖлҸҷ | в–· ITмӮ°м—… кІҪкё°лҸҷн–Ҙкіј л°ҳлҸ„мІҙмӮ°м—… кІҪкё°м—җ мҳҒн–Ҙмқ„ л°ӣмқҢ |

| мЈјмҡ”м ңн’Ҳ | в–· PLDл°ҳлҸ„мІҙ мң нҶөВ·мҶ”лЈЁм…ҳ м ңкіө: м„ёкі„ 1мң„ PLDл°ҳлҸ„мІҙ м—…мІҙ мһҗмқјл§ҒмҠӨмӮ¬ л“ұмңјлЎңл¶Җн„° PLDл°ҳлҸ„мІҙлҘј кіөкёүл°ӣм•„ мң нҶө л°Ҹ кё°мҲ м§Җмӣҗ(л°ҳлҸ„мІҙ м„Өкі„) мҶ”лЈЁм…ҳ м ңкіө |

| мӢӨм ҒліҖмҲҳ | в–· мһҗмқјл§ҒмҠӨ(Xilinx)мӮ¬мқҳ PLD м ңн’Ҳ мқём§ҖлҸ„ мғҒмҠ№мӢң мҲҳнҳң в–· ITм ңн’Ҳ к°ңл°ң мЈјкё° лӢЁм¶•мӢң мҲҳнҳң |

| лҰ¬мҠӨнҒ¬ | в–· мөңлҢҖмЈјмЈј ліҙмң м§Җ분мқҙ 10.7%лЎң лӮ®мқҢ |

| мӢ к·ңмӮ¬м—… | в–· 진н–үмӨ‘мқё мӢ к·ңмӮ¬м—… м—ҶмқҢ |

мң„мқҳ кё°м—…м •ліҙлҠ” н•ңкөӯнҲ¬мһҗкөҗмңЎм—°кө¬мҶҢк°Җ мӮ¬м—…ліҙкі м„ң, IR мһҗлЈҢ, лүҙмҠӨ, м—…кі„лҸҷн–Ҙ л“ұ н•ҙлӢ№ кё°м—…мқҳ к°Ғмў… мһҗлЈҢлҘј м°ёкі н•ҙ м§ҖмҶҚм ҒмңјлЎң м—…лҚ°мқҙнҠё н•©лӢҲлӢӨ. л§Өм»ӨмҠӨмқҳ м •ліҙлҠ” 2015л…„ 05мӣ” 19мқјм—җ мөңмў… м—…лҚ°мқҙнҠё лҗҗмҠөлӢҲлӢӨ.

(мһҗлЈҢ : м•„мқҙнҲ¬мһҗ www.itooza.com)

[л§Өм»ӨмҠӨ] н•ң лҲҲм—җ ліҙлҠ” нҲ¬мһҗм§Җн‘ң

(лӢЁмң„: м–өмӣҗ)

[л§Өм»ӨмҠӨ] мЈјмҡ”мЈјмЈј

| м„ұ лӘ… | кҙҖ кі„ | мЈјмӢқмқҳ мў…лҘҳ | мҶҢмң мЈјмӢқмҲҳ л°Ҹ м§Җ분мңЁ | л№„кі | |||

|---|---|---|---|---|---|---|---|

| кё° мҙҲ | кё° л§җ | ||||||

| мЈјмӢқмҲҳ | м§Җ분мңЁ | мЈјмӢқмҲҳ | м§Җ분мңЁ | ||||

| мӢ лҸҷмІ | ліёмқё | ліҙнҶөмЈј | 708,586 | 4.39 | 708,586 | 4.39 | - |

| м„ұмў…лҘ | нҠ№мҲҳкҙҖкі„мқё | ліҙнҶөмЈј | 478,715 | 2.96 | 478,715 | 2.96 | - |

| м„ұкё°нҷҚ | нҠ№мҲҳкҙҖкі„мқё | ліҙнҶөмЈј | 30,000 | 0.19 | 30,000 | 0.19 | - |

| м„ұкё°мӣ… | нҠ№мҲҳкҙҖкі„мқё | ліҙнҶөмЈј | 30,000 | 0.19 | 30,000 | 0.19 | - |

| мөңмҠ№к·ј | нҠ№мҲҳкҙҖкі„мқё | ліҙнҶөмЈј | 486,000 | 3.01 | 486,000 | 3.01 | - |

| кі„ | ліҙнҶөмЈј | 1,733,301 | 10.74 | 1,733,301 | 10.74 | - | |

| - | - | - | - | - | - | ||

лҚ” мўӢмқҖ кёҖ мһ‘м„ұм—җ нҒ° нһҳмқҙ лҗ©лӢҲлӢӨ.